VIAVI Solutions

#### Data Sheet

# VIAVI ONT-600 400G CFP8 Modules

#### Introduction

400G technology is already being deployed under the emerging IEEE standard P802.3bs. With this innovation, test and measurement needs arise – from module development and validation, through hardware and IP integration to service deployment. The ONT 400G addresses all of these and provides a complete, scalable test solution for the whole 400G ecosystem. It is ready for the 400G challenges today and future needs such as FlexO, FlexE and future OTN.

# **Solution Highlights**

- Complete and comprehensive application coverage for troubleshooting physical layer & signal integrity issues through PCS/FEC to full Ethernet traffic. Real-world traffic applications allow full component validation in true application cases. No more limited and misleading unframed testing.

- Helps quickly identify the root cause of errors, especially in the physical layer, with novel applications including advanced error analysis. Quickly identify operating margin with real FEC characteristics, no more blind guessing based on eye diagrams and raw BER.

- Applications to cover complete IC and module validation from unframed SERDES performance validation and diagnostics through to comprehensive coverage of complex IP blocks like FEC/PCS, packet throughput and QoS.

- Integrated tools for complete CFP8 validation and turn up. Quickly validate operating margin and characteristics.

- Supports electrical access via 16 x NRZ Electrical Adapter, and PAM-4 via 8 x PAM-4 Electrical Adapter.

- Ready to support future form factors like QSFP-DD, OSFP etc.

- Support for future flexible bandwidth needs such as FlexO and FlexE with the 5 x 100G QSFP28 ports dedicated to scalable bandwidth including bonding, sub-rating and channelization. Current and future software options extend the applications addressed by ONT 400G, protecting your investment.

- Novel tools and accessories help troubleshoot the challenging areas of PAM-4 and FEC, core technologies which underpin 400G and future high-speed telecom and datacomm interfaces. Test grade adapters and accessories are perfectly matched to the ONT application, no more worries if 3rd party interconnects impact test results.

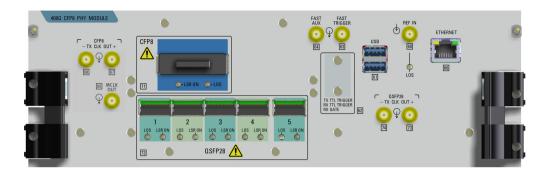

Figure 1. ONT 400G Front Panel

#### **General Information**

The ONT-600 400G CFP8 Module is a three-slot module and is compatible with the ONT-603, -606 and -612 mainframe products. The module is adequately powered and cooled by the mainframe.

# **Front Panel Interfaces**

- MSA compliant CFP8 slot

- Five MSA compliant QSFP28 slots provide support for upcoming FlexE and FlexO applications.

- A range of electrical I/O to support comprehensive test capabilities.

| Signal                        | Туре       | Connector    | Coupling | Impedance | Amplitude/ Sensitivity                       |

|-------------------------------|------------|--------------|----------|-----------|----------------------------------------------|

| Clock input                   | Unbalanced | SMA female   | AC       | 50 Ω      | 200 500 mVpp                                 |

| Tx Clock output               | Balanced   | 2xSMA female | AC       | 100 Ω     | Bal.: 800 mVpp typ.<br>Unbal.: 400 mVpp typ. |

| MCLK output                   | Unbalanced | 2xSMA female | AC       | 100 Ω     | Bal.:800 mVpp typ.Unbal.:400 mVpp typ.       |

| Fast AUX out (for future use) | Unbalanced | SMA female   | AC       | 50 Ω      | 400 mVpp typ.                                |

#### **CFP8 Interface – Description & Capabilities**

- CFP8 interface in accordance with CFP8 MSA, based on AUI-16 (16 lanes of 25G NRZ differential TX and RX)

- Indicator LEDs for 'Laser on' and LOS with respect to CFP8 transponder.

- Interface supports bit rates from 400 Gbps to 488 Gbps in 1 kbps steps (0.00025 ppm)

- Clocking source can be internal (mainframe reference) or external reference via front panel connector on the 400G blade. A jitter filter can be switched in and out in certain modes to allow phase modulated signals as the clock source.

# Supported Clocking Modes

|                                 |                                                      |                                              | Delta [ppm] |        | Jitter  | _                                                                                                                                                                              |  |

|---------------------------------|------------------------------------------------------|----------------------------------------------|-------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock source mode               |                                                      | Range                                        | Resolution  | filter | Comment |                                                                                                                                                                                |  |

|                                 | Internal (default                                    | t)                                           | +/- 500     | 0.01   | N/A     | —                                                                                                                                                                              |  |

|                                 | From Rx                                              |                                              | +/- 500     | 0.01   | yes     | -                                                                                                                                                                              |  |

| Clock input<br>"Direct Ref. In" | Jitter Filter<br>Mode<br>(Default: Low<br>bandwidth) | Mode bandwidth<br>Default: Low (BW ≤ 100 Hz) |             | 0.01   | yes     | ONT 400G is clocked via jitter filter and synthesizer.<br>Jitter Filter Modes: Low (< 100 Hz), High                                                                            |  |

|                                 |                                                      | High<br>bandwidth<br>(BW ~1 MHz)             | N/A         | N/A    | no      | Clock direct to ONT 400G. This setting allows for jitter<br>modulation. Lowest intrinsic jitter.<br>Limitations:<br>• No delta ppm possible.<br>• User bit rate not supported. |  |

# **RX Offset Range and Measurement**

| Parameter                        | Range / value                                                      |

|----------------------------------|--------------------------------------------------------------------|

| Rx offset range                  | Normal range: +/- 500 ppm                                          |

| RX Offset fallge                 | Note – within this range measurements will be accurate and stable. |

| Rx offset measurement range      | Normal range: +/- 500 ppm                                          |

| Rx offset out-of-range threshold | +/- 200 ppm                                                        |

| Rx offset out-of-range threshold | Electrical lane speed /40 Unbalanced                               |

| Offset measurement resolution    | 0.01 ppm                                                           |

| Offset measurement accuracy      | +/- 0.005 ppm <sup>1</sup>                                         |

1. Not taking timebase error into account.

| <u>File Applications Re</u>                                                                 | esults <u>T</u> ools <u>H</u> e                                                         | lp                                           |                                    |                                           |          |                                                                        |               | Clock Overview                                           |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|-------------------------------------------|----------|------------------------------------------------------------------------|---------------|----------------------------------------------------------|

| VIAVI                                                                                       | ONT-600<br>400G Mo                                                                      | dule OFC-01                                  | Port 1                             | Location: ON<br>Application: r            |          | 1200 Slot 1-3.1 10.49.7                                                | 4.11          | Module Time: 10:47 MESZ<br>Disk: 4,4GB of 7,2GB free     |

| RX Porti CFP8<br>Interface V<br>LDS<br>Frea. Rea.                                           | Config.<br>Status<br>Overview<br>Rx Optical<br>Power<br>Tx Optical<br>Power             | Bitrate:<br>Interface:                       | cks / Trig. CD<br>425 Gb/s [400Gig | AUI-16 Patt.<br>E]<br>CFP8 [71]           | CDAUI-16 | User Bitrate:<br>MDIO Bitrate:                                         | ups CFP8      | Gb/s                                                     |

| Total Opt. Power:<br>4.5 dBm<br>Frequency:<br>425.000.001 kHz<br>Frequ. Offset:<br>0.00 ppm | Rx Errors/<br>Alarms<br>Rx BER<br>Estimation<br>Tx Errors/<br>Alarms<br>Tx Lane<br>Skew | TX<br>Total Opt. Power:<br>Frequency Offset: | .13                                | +4,5 dBm<br>+ wer Measuremen Transition F | Ramp     | RX<br>Total Opt. Power:<br>LOS<br>Frequency Offset:<br>Out of<br>Range |               | +4.5 dBm<br>+17<br>er Measurement<br>00 ppm<br>+200 +500 |

|                                                                                             | Tx Freq.<br>Variation<br>Rx Bit<br>Capture<br>Rx Error<br>Analysis<br>Stress<br>Test    | Clock Source:                                | Internal (from Clos                | ck Module]                                | ~        | Frequency:<br>Timing Lane:                                             | 425.000.001 I |                                                          |

| Payload Patt. Loss<br>Bit Error<br>Errored Zero<br>Errored One                              | Help                                                                                    |                                              | Default                            |                                           |          |                                                                        | Default       |                                                          |

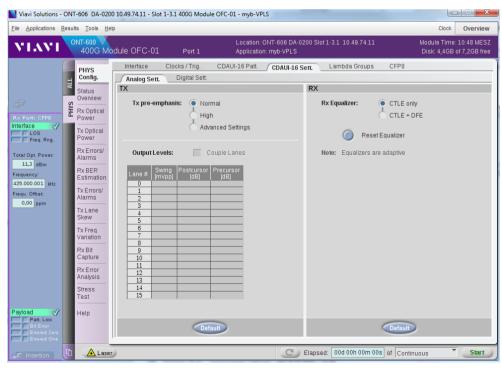

Fig 2. TX/RX Physical Parameters

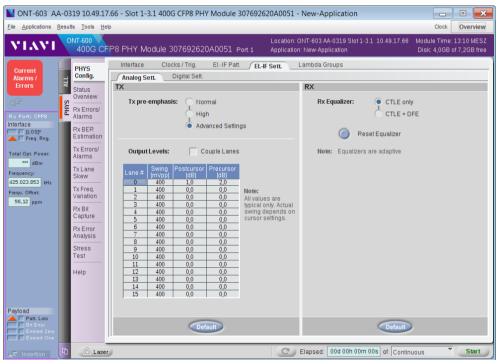

#### **Electrical Module Settings**

Clock accuracy is directly linked to reference oscillator on mainframe or any user supplied clocking source.

Module power class – modules of up to 16 W can be powered and cooled in environments of up to 40° C ambient temperature. Modules up to 20 W can be supported if the airflow into the mainframe is unobstructed and temperature no more than 23° C ambient. The application GUI reports the current and power drawn by the module.

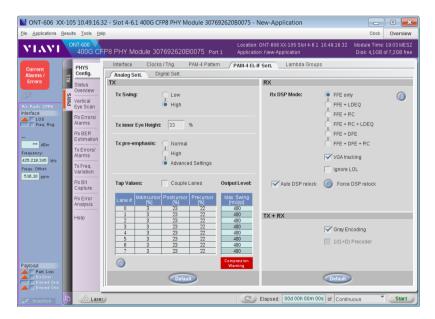

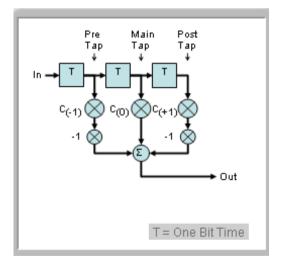

The user has control over aspects of TX and RX parameters including equalizer settings and voltage swing. The default settings are carefully matched to the needs of normal CFP8 modules. The user can vary the TX swing and pre-emphasis and address the RX equalizer DFE (Decision Feedback Equalizer) and CTLE (Continuous Time Linear Equalizer) mode (CTLE only, or CTLE + DFE). The settings can be applied to all 16 AUI lanes together or independently as required. Each individual AUI-16 lane can be independently inverted at both the RX and TX side.

- Module power supply voltage default is 3.3 V as per MSA

- The ONT reports all core CFP8 parameters including both TX / RX clock offset and optical power (if supported by the CFP transponder & MDIO)

- Module supports transponder reference clocks of /40 and /160 rates with the default set to /160.

- For every clocking mode TX LTI (loss of timing information) clock status is provided.

- Module supports transponder TX output clocks of /40 and /160 rates with the default set to /40.

- TX and RX MCLK is supported in accordance with the CFP8 MSA.

- RX clock recovery is supported on all AUI-16 lanes default is the lowest number lane with a valid clock content, user can manually select any desired lane.

Fig 3. Analog TX and RX Settings

## **MDIO Functions**

|                | Normal (bus runs at set speeds and supports auto-increment read/write)                                                                              |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIO modes     | Relaxed (bus timing is gentler, every read/write is addressed and timing between commands is extended to support modules with limited capabilities) |

|                | Off (MDIO bus off – no MDIO commands; read, write, module RX and TX optical power reporting etc. not supported).                                    |

| MDIO bus speed | Default 4 MHz, "hardware validation" option supports 0.5, 0.8, 1.0, 1.333, 2.0, 2.29, 2.66, 3.2 and 4.0 MHz bus clocking                            |

#### **Unframed Testing**

| Interface         | AUI-16 NRZ                                                                                             |

|-------------------|--------------------------------------------------------------------------------------------------------|

| Pattern modes     | Same pattern on all 16 lanes, user settable pattern per lane, pattern offset, staggered                |

| Patterns          | PRBS31, PRBS23, PRBS15, PRBS13, PRBS9, PRBS7 and inverted, 8 Byte DW, SSPR Stress Pattern, square wave |

| TX/RX lane modes  | Mute, invert, free lambda group lane mapping                                                           |

| BER Estimation    | Per virtual lane, per lambda group                                                                     |

| Error Stress Test | Automatic test through all available test patterns / offset / skew values                              |

#### CFP8 Hardware Validation (Option 3076/97.30)

- User selectable bit rate within the range of 400 ... 488 Gbps

- Module voltage: from 2.5 V to 3.7 V in 50 mV steps

- MDIO clock/data voltage swing: 1.0 to 1.4 V in 50 mV steps

- Advanced CFP8 MDIO debug functions: power supply variation, MDIO R/W, MDIO dump, HW control, remote and local loopback (if supported by CFP8)

#### Dynamic Skew Generation (Option 3076/97.32)

The optional dynamic skew application allows individual lanes to be skewed backward and forward. The dynamic skew generation is supported in higher layer applications including PCS/FEC and Ethernet.

Skew variation is supported for all Tx clocking modes.

| Dynamic skew | Range / value                                          |

|--------------|--------------------------------------------------------|

| Range        | +/- 512 bit with respect to unskewed 'reference' lanes |

| Resolution   | 10 mUI                                                 |

| Slope        | 10 10,000 mUI/s                                        |

| Mode         | Manual, triangular                                     |

| Viavi Solutions -                                                                                                                | ONT-606 DA-020                                                                                                                                                                | 0 10.49.74.11 - Slot 1-3.1                       | 400G Module OFC-0                                                                                                                            | 1 - myb-VPLS                                            |                         |            |                                              |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------|------------|----------------------------------------------|

| File Applications                                                                                                                | <u>R</u> esults <u>T</u> ools <u>H</u> e                                                                                                                                      | Hp .                                             |                                                                                                                                              |                                                         |                         | Clock      | Overview                                     |

| VIAVI                                                                                                                            | ONT-600<br>400G M                                                                                                                                                             | dule OFC-01                                      | Port 1                                                                                                                                       | Location: ONT-606 DA-0200 Slot<br>Application: myb-VPLS | 1-3.1 10.49.74.11       |            | : 10:52 MESZ<br>of 7,2GB free                |

| Ax Port OFPO<br>Interface V<br>Freq Reg<br>Tatal Opt Power<br>113 dBm<br>Frequency:<br>225 000.001 H/z<br>Frequency:<br>0.00 ppm | PHYS<br>Config.<br>Status<br>Overview<br>Prover<br>Tx Optical<br>Power<br>Rx Errors/<br>Alarms<br>Rx BER<br>Estimation<br>Tx Errors/<br>Alarms<br>Tx Lane<br>Skew<br>Tx Freg. | At least one lane shou<br>Positive skew value => | Initializing<br>Ready<br>abling stev generation<br>id be solected.<br>Lane is late with respe-<br>blane is early with resp<br>Manual<br>1000 |                                                         | Select Lane             |            | 02<br>03<br>04<br>05<br>05<br>07<br>08<br>09 |

|                                                                                                                                  | Variation<br>Rx Bit<br>Capture<br>Rx Error<br>Analysis                                                                                                                        | Slope: +/-<br>Current Skew:                      | 100 mU                                                                                                                                       | mUI/s                                                   |                         |            | 012<br>013                                   |

| Payload 🗸                                                                                                                        | Stress<br>Test<br>Help                                                                                                                                                        | G Skew (All selecte                              | id lanes)                                                                                                                                    |                                                         |                         |            |                                              |

| Bit Error<br>Errored Zero<br>Errored One                                                                                         |                                                                                                                                                                               |                                                  |                                                                                                                                              | Default                                                 |                         |            |                                              |

| F Insertion                                                                                                                      | 🗈 🛕 Lase                                                                                                                                                                      | 5                                                |                                                                                                                                              | C Elapsed                                               | 1: 00d 00h 00m 00s of ( | Continuous | Start                                        |

Fig 4. Dynamic Skew Variation on selected lane(s)

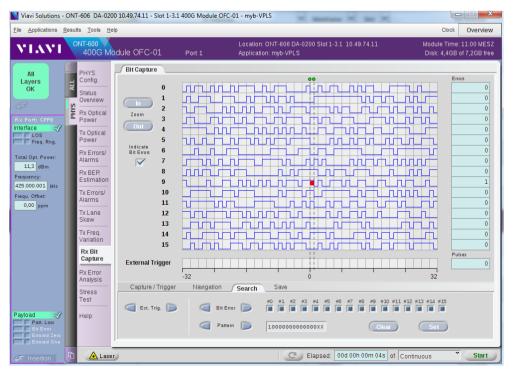

#### Advanced Error Analysis (Option 3076/97.31)

| In-depth error analysis | Error capture per lane, burst size and error pattern analysis, error distance and bit slip analysis |

|-------------------------|-----------------------------------------------------------------------------------------------------|

| Bit capture             | Capture all 16 AUI lanes                                                                            |

| Memory depth            | 512 kb per lane                                                                                     |

| Bit capture trigger     | Bit error, pattern, external                                                                        |

Fig 5. Capture function on the physical layer

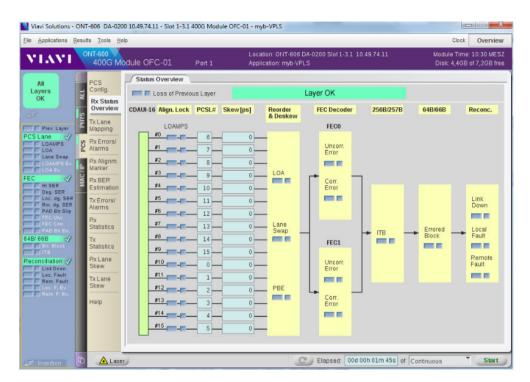

#### **400GE Ethernet Testing**

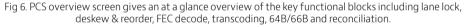

### **PCS Layer Specifications**

| Each lane is clocked from common clock                 |                                                                                                                                    |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| TX ignore link faults                                  | On/off                                                                                                                             |

| FEC Bypass Correction and Indication                   | On/off                                                                                                                             |

| Lambda Groups assignment                               |                                                                                                                                    |

| TX/ alignment marker and RX reference alignment marker | Fully editable                                                                                                                     |

| RX Status Overview                                     | LOAMPS indication per lane, PCS Lane#, Lane Swap alarm,<br>FEC correctable/uncorrectable, ITB, Errored Block, Link Down, L/R Fault |

| Fully flexible lane mapping                            |                                                                                                                                    |

| RX errors and alarms                                   | LOAMPS, LOA, Lane Swap, SER, Link down, FEC corr./uncorr. ones and zeroes                                                          |

| Full view of received alignment markers                |                                                                                                                                    |

| Bit Error Rate Estimation for given confid             | dence level (aggregate and per lane)                                                                                               |

| TX Alarm/Error insertion                               | LOAMPS, SER, LF/RF                                                                                                                 |

| RX Block and FEC Error Statistics                      | Table and graphic format                                                                                                           |

| Lane Skew static                                       | Static up to 64,000 bits                                                                                                           |

| Lane Skew dynamic (option)                             | Up to +/- 512 UI in 30 mUI steps                                                                                                   |

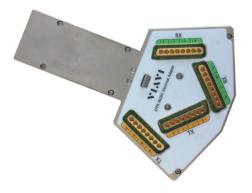

#### **MAC/IP Layer Specifications**

Fig 7. MAC/IP Traffic Generation

| Up to 256 flows with IP and/or MPLS                    | , one user-defined traffic profile,    |                                                                                           |  |  |  |  |

|--------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Traffic profile                                        |                                        | Constant load, bursty, ramp, IMIX;<br>bandwidth 0.1 400,000,000 Mbps, back to back frames |  |  |  |  |

| VLAN tags                                              | up to 2, VLAN tags user-defined        |                                                                                           |  |  |  |  |

| MPLS labels                                            | up to 5, user defined                  |                                                                                           |  |  |  |  |

| Ethernet frame sizes                                   | 64 bytes to 10,000 bytes               | 64 bytes to 10,000 bytes                                                                  |  |  |  |  |

| User-defined payload (up to 124 byte                   | s for MAC, up to 64 bytes for IP), use | r-defined preamble, and SFD                                                               |  |  |  |  |

|                                                        | Resolution                             | frame                                                                                     |  |  |  |  |

| Service Disruption measurement                         | Result display                         | number of frames, nanoseconds                                                             |  |  |  |  |

| Transfer Delay measurement with calibration capability | Resolution                             | Resolution 0.1 ns                                                                         |  |  |  |  |

| Throughput measurement and fram                        | e statistics                           |                                                                                           |  |  |  |  |

| Alarm/Error insertion and analysis                     | FCS, runt, oversized, invalid SFD, I   | P header error in single, burst and rate modes, per flow                                  |  |  |  |  |

| TX Test Frame Errors                                   | Frame loss, mis-insertion, swap, d     | Frame loss, mis-insertion, swap, duplication                                              |  |  |  |  |

| Capture Modes                                          | Direct, filtered; buffer size: 128 kB  | Direct, filtered; buffer size: 128 kByte; offline analysis with Wireshark                 |  |  |  |  |

| Auto Test Modes                                        | Preamble transparency, throughp        | ut                                                                                        |  |  |  |  |

# 400G Ethernet FEC Validation (Option 3076/93.41)

FEC Validation application gives comprehensive overview of the errored symbols in a given codeword, a good indicator of link margin and module performance.

The FEC stress test has wide ranging applications including validation and verification of FEC receiver functionality. It also has novel applications for verifying power supply stability of ASIC and FPGA FEC implementations. Every correctable error utilizes deep layers of XOR based logic, and the fast switch of this logic can cause fast changes in power draw inside the ASIC/FPGA. The ONT FEC Stress application allows aggressive patterns to be generated that can maximally stress the power supply dynamics.

The capabilities of the FEC Validation application range from simple injection of individual 256B/257B Block Errors and errors in a symbol within a FEC codeword through to complex walking patterns that can generate the maximum spread of potential correctable errors within a codeword.

| NT-603 AA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -0319 10.49.1                                                                                                                                                                                                                | 7.66 - Slot 1-3.1 400G C | FP8 PHY Module 3076                        | 92620A0051 - N | lew-Application                                                        |                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------|----------------|------------------------------------------------------------------------|------------------------------------------------------|

| <u>File</u> <u>Applications</u> <u>R</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | esults <u>T</u> ools <u>H</u>                                                                                                                                                                                                | elp                      |                                            |                |                                                                        | Clock Overview                                       |

| VIAVI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ONT-600<br>400G C                                                                                                                                                                                                            | FP8 PHY Module 307       | 692620A0051 Port 1                         |                | T-603 AA-0319 Slot 1-3.1 10.49.17.66<br>New-Application                | Module Time: 15:33 MESZ<br>Disk: 4,0GB of 7,2GB free |

| All<br>Layers<br>OK<br>Prev. Layer<br>PCS Lane<br>COAMPS EV<br>LOAMPS EV<br>L | PCS<br>Config.<br>Rx Status<br>Overview<br>Mapping<br>Rx Errors/<br>Alarms<br>Rx BER<br>Px Alignm.<br>Marker<br>Rx BER<br>Px Alignm.<br>Marker<br>Rx Statistics<br>Tx Statistics<br>Tx Statistics<br>Tx Lane<br>Skew<br>Help | 64B / 66B FEC Sta        | t <b>istics</b> FEC Error Sta<br>gram View |                | Number of symbol errors per cod<br>Percentage is with respect to all c | eword.                                               |

| . Electrica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Lase                                                                                                                                                                                                                         | er l                     |                                            | C EI           | apsed: 00d 00h 35m 34s of Contin                                       | uous Stop                                            |

| 🗲 Insertion 🛛                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                              |                          |                                            |                | of Contain                                                             |                                                      |

Fig8. FEC error statistics reports number of symbols in error per codeword as a count and as a percentage of the total errors

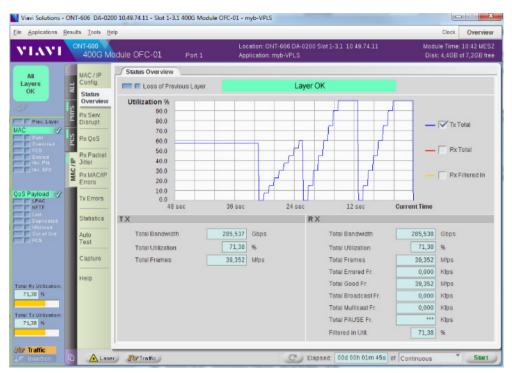

# CFP8 16 x 25G Electrical Adapter (Option 3076/96.43)

The CFP8 16 x 25G NRZ adapter allows access to the electrical AUI-16 interface.

#### 400G Electrical Adapter Specifications

| NRZ lanes             | 2 x differential; Impedance: 100 <b>Ω</b> ;<br>Coupling: AC |

|-----------------------|-------------------------------------------------------------|

| TX swing              | 200 1000 mV (typical)                                       |

| TX Pre-emphasis       | Normal, high, user-defined                                  |

| RX Equalizer          | CTLE only, DLE + DFE                                        |

| Termination impedance | 100 <b>Ω</b> typical, +/- 25 <b>Ω</b>                       |

| Connector type        | 8 x 1 (manufacturer H+S), 2.92 mm                           |

Fig 9. CFP8 16 x 25G NRZ adapter

Fig 10. Advanced settings for 16 x NRZ TX lane pre-emphasis

Hint: For the connection between the 16 x 25 NRZ adapter and the customer DUT, VIAVI recommends using appropriate electrical cables from the H+S MXP50 series. These are not supplied by VIAVI since they must match the electrical connectors of the customers' evaluation boards.

# Adapters 16 x NRZ to 8 x PAM-4

#### CFP8 8 x 50G PAM-4 Electrical Adapter (Option 3076/96.44)

The PAM-4 Electrical Adapter is ready to provide in-depth evaluation of early 400G PAM-4 components. These are typically accessed via evaluation boards. Other applications include host and module compliance tests.

The adapter transforms the 16 AUI NRZ lanes into 8 PAM-4 electrical lanes.

#### Accessories

2 short loopback cables (Manufacturer H+S) are delivered together with the PAM-4 Adapter. These are used for the internal automatic de-skew calibration process, they are not meant to be connected to a customer DUT.

Fig 11. CFP8 - 8 x 50G PAM-4 electrical adapter and calibration cables

Fig 12. (8 x 1) connector by H+S

#### QSFP-DD Adapter (Option 3076/96.45)

The QSFP-DD Adapter is esigned to house a standard QSFP-DD transponder and provides an 8 x 50G PAM-4 signal.

QSFP-DD Power classes 1 – 7 (max. QSFP-DD Power 14 W)

Supports QSFP-DD Rev. 3.0 Accessory: QSFP-DD Loopback Adapter

Fig 13a. QSFP-DD adapter

Fig 13b. QSFP-DD loopback adapter

Fig 14a. OSFP adapter

Fig 14b. OSFP loopback adapter

#### OSFP Adapter (Option 3076/96.46)

The OSFP Adapter is esigned to house a standard OSFP transponder and provides an 8 x 50G PAM-4 signal.

OSFP Power classes 1 – 5 (max. OSFP Power 16 W)

Supports OSFP Module Specification 1.12

Accessory: OSFP Loopback Adapter

### Adapter Specifications PAM-4 electrical, QSFP-DD, OSFP

| PAM-4 lanes            | AUI-8 differential lanes, 53.125 or 51.5625 Gbps        |

|------------------------|---------------------------------------------------------|

| Modulation TX/RX       | PAM-4                                                   |

| Impedance              | 100 Ω                                                   |

| Coupling               | AC (electrical adapter), DC (QSFP-DD and OSFP adapters) |

| Voltage swing          | 200 1000 mV (typical)                                   |

| Connectors             | Four 8 x 1, H+S (PAM-4 electrical adapter only)         |

| Frequency offset range | +/- 250 ppm                                             |

Fig 15. Analog settings for PAM-4 adapters

Fig 16. Detailed view of TX pre-emphasis settings (per lane or "all lanes")

#### PAM-4 TX Characteristics

The TX signal can be set to a standard default value that covers most practical cases. In addition, GUI allows access to advanced pre-emphasis values via the above dialog. Output voltage will be in the range of 200 .... 1000 mVpp typical, depending on settings. Dynamic skew insertion is disabled.

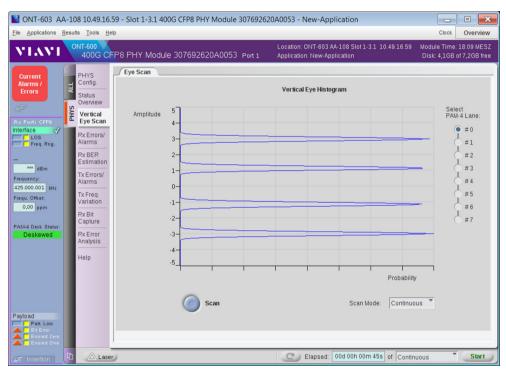

#### PAM-4 RX Characteristics

Supports the following DSP Modes: FFE (feed forward equalizer), LDEQ (level-dependent equalizer), RC (reflection cancellation), DFE (distributed feedback equalizer).

#### Supported applications via PAM-4 adapter

Full range of available ONT 400G applications, including unframed patterns, PCS/FEC layer, MAC/IP traffic.

Fig 15. Screen: PAM-4 Vertical Eye Scan quickly identifies issues with PAM-4 RX and TX setups

Advanced Error Analysis (Option 3076/97.31) can be used together with the PAM-4 adapter to quickly identify issues with areas like error burst length, critical for PAM-4 based interfaces with FEC:

| Ordering Information: |                                                                                                             |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 400G Modules          |                                                                                                             |  |  |  |

| 3076/92.62            | 400G CFP8 Phy Module – CFP8 slot, 5 x QSFP28 slots, full physical layer test capabilities, 400G Ethernet SW |  |  |  |

| 3076/92.64            | 400G CFP8 Data Module – CFP8 slot, 5 x QSFP28 slots, 400G Ethernet SW                                       |  |  |  |

| 3076/92.63            | QFlex Data Module – 5 x QSFP28 slots, to be combined with at least one SW option out of FlexE or FlexO      |  |  |  |

| 3076/92.65            | CFP8 QFLEX Data Module - CFP8 slot, 5 x QSFP28 slots, no SW included                                        |  |  |  |

| Options and acces     | sories                                                                                                      |  |  |  |

| Options available     | on DATA and PHY Modules                                                                                     |  |  |  |

| 3076/97.30            | CFP8 Hardware Validation SW                                                                                 |  |  |  |

| 3076/97.41            | 400G Ethernet FEC Validation SW                                                                             |  |  |  |

| 3076/97.45            | 200G Ethernet                                                                                               |  |  |  |

| 3076/97.46            | 200GE FEC Validation                                                                                        |  |  |  |

| 3076/97.50            | FlexE 100GBase-R SW with clients up to 100GE                                                                |  |  |  |

| 3076/97.51            | FlexE FEC Validation                                                                                        |  |  |  |

| 3076/97.60            | OTN FlexO OTUCn Bulk                                                                                        |  |  |  |

| 3076/97.62            | OTN FlexO FEC Validation                                                                                    |  |  |  |

#### Options available on CFP8 PHY Module only

| 3076/97.31 | CFP8 Advanced Error Analysis SW |

|------------|---------------------------------|

| 3076/97.32 | CFP8 Dynamic Skew Generation SW |

| Accessories for CFP8 PHY Module only |                                     |  |

|--------------------------------------|-------------------------------------|--|

| 3076/96.43                           | CFP8 16x25G Electrical Adapter      |  |

| 3076/96.44                           | CFP8 8x50G PAM-4 Electrical Adapter |  |

#### Accessories for CFP8 PHY and Data Modules

| Accessories for err of the and bata modules |                                     |

|---------------------------------------------|-------------------------------------|

| 3076/96.45                                  | CFP8 to QSFP-DD 8x50G PAM-4 Adapter |

| 3076/96.46                                  | CFP8 to OSFP 8x50G PAM-4 Adapter    |

Contact Us +1 844 GO VIAVI (+1 844 468 4284)

To reach the VIAVI office nearest you, visit viavisolutions.com/contacts.

© 2018 VIAVI Solutions Inc. Product specifications and descriptions in this document are subject to change without notice. 400g-ds-opt-tm-ae 30186280 902 0518